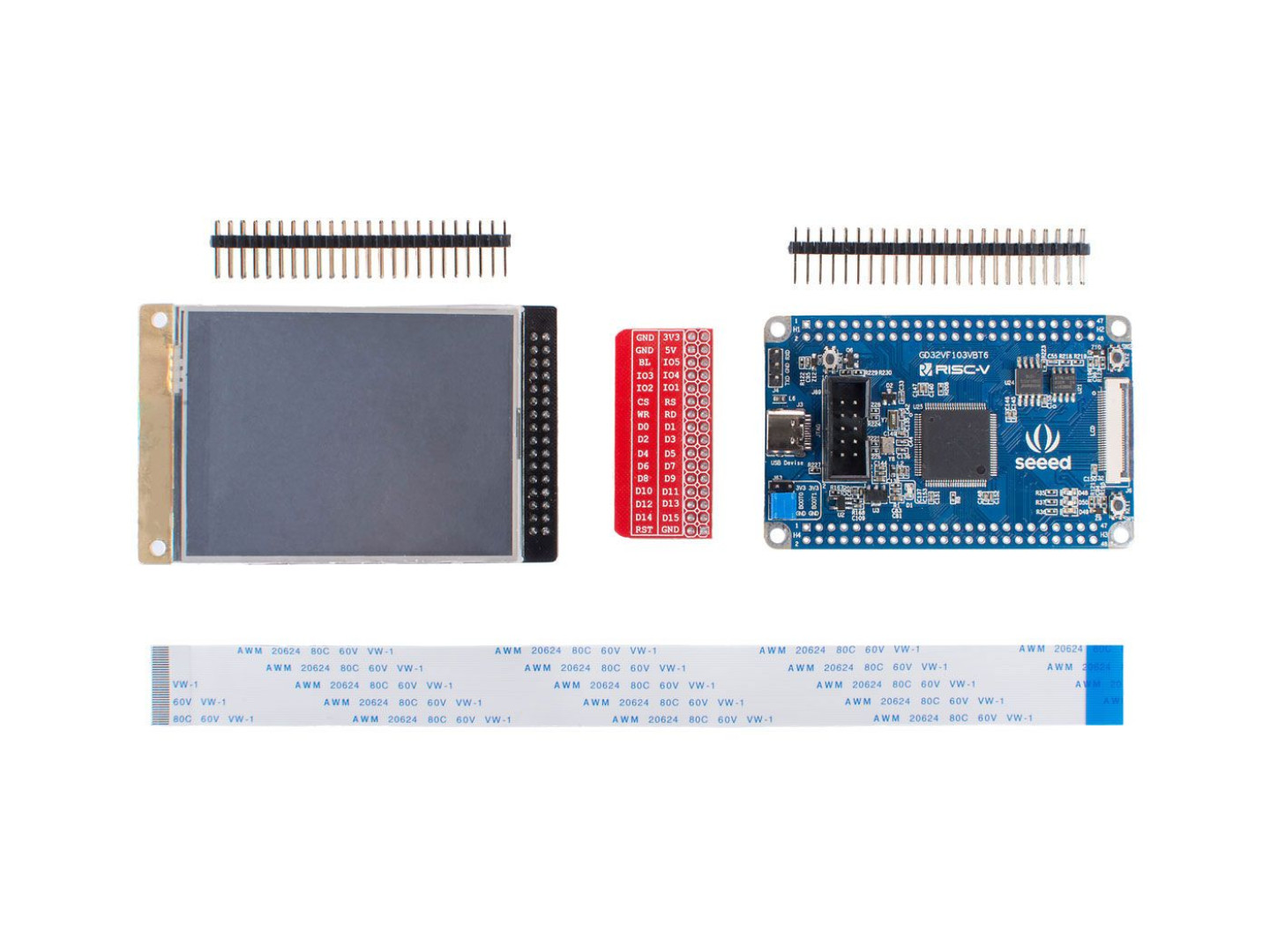

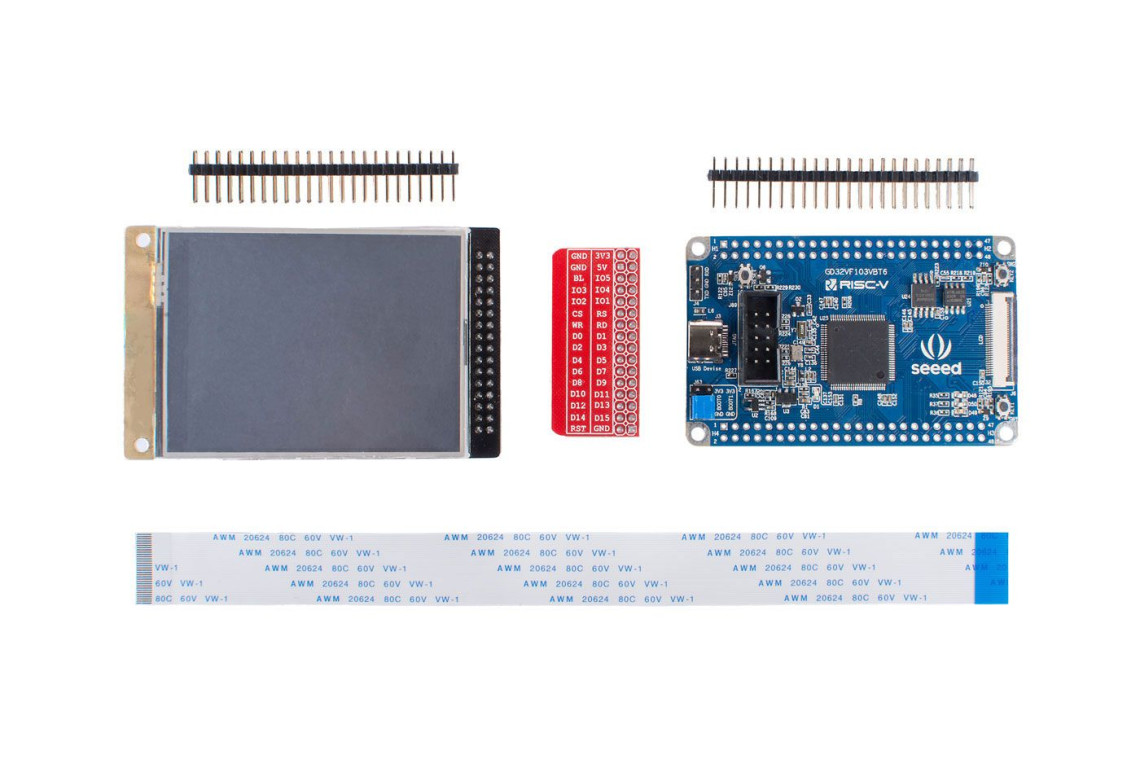

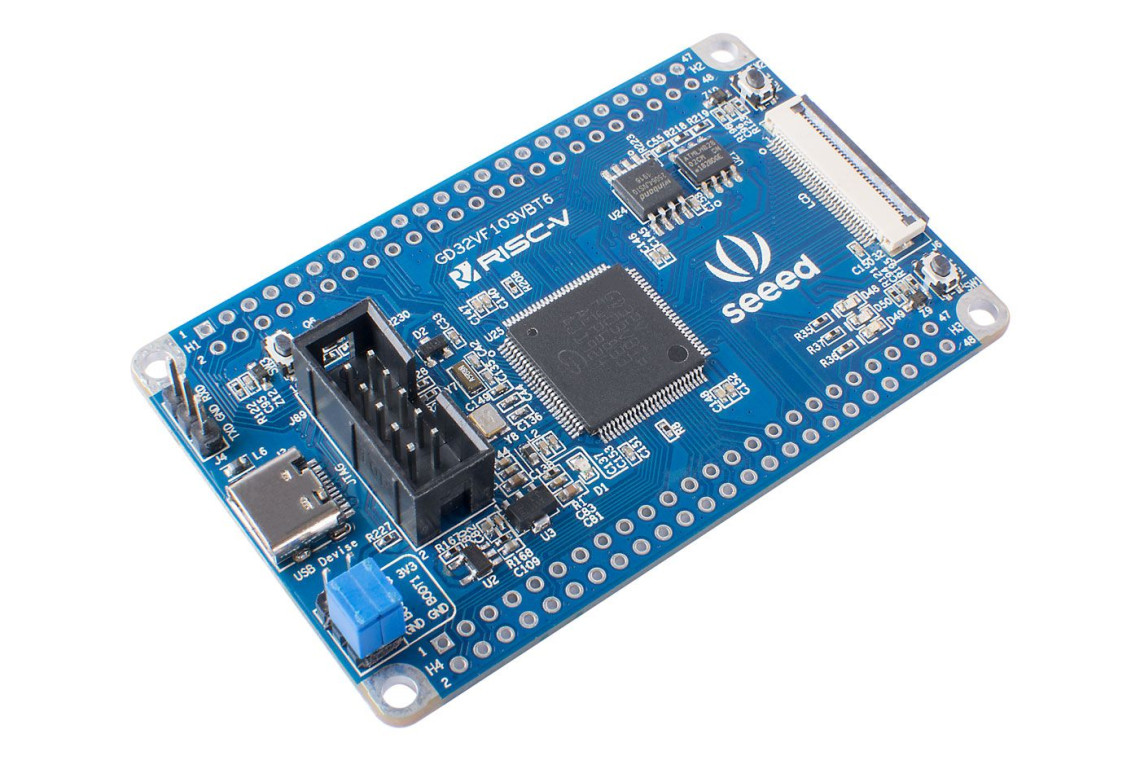

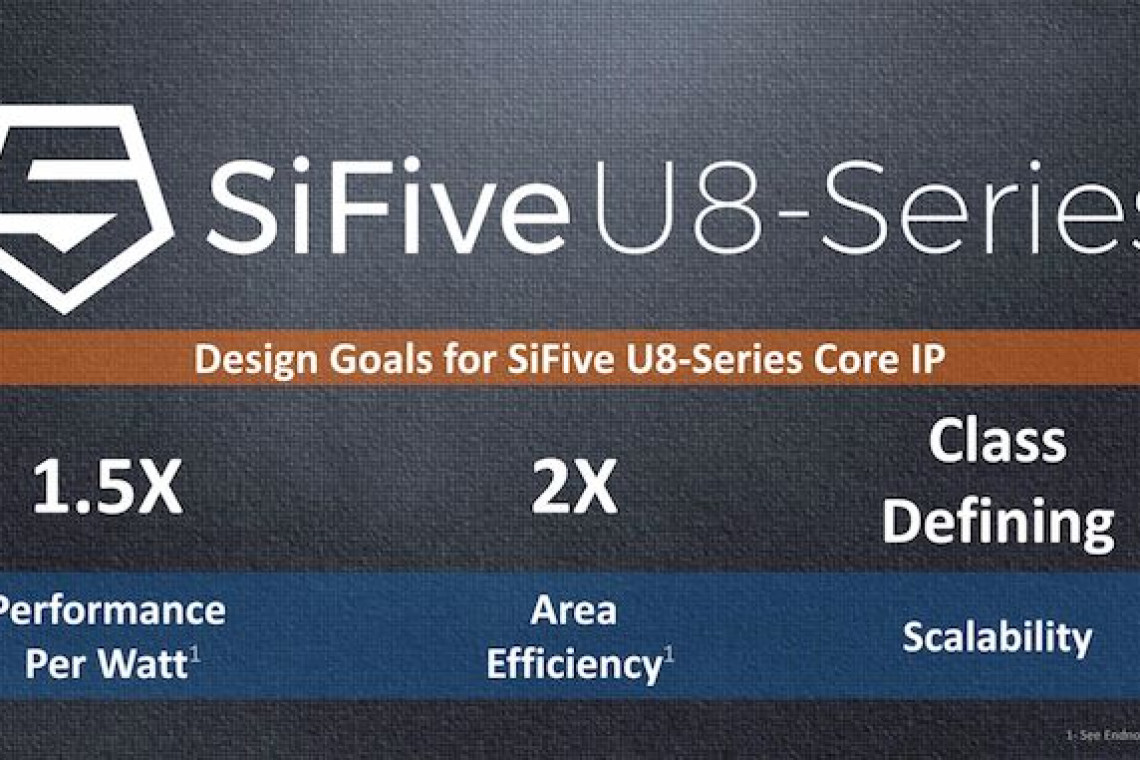

Lancé officiellement en octobre, le projet européen Horizon 2020 De-RISC (infrastructure fiable en temps réel pour les ordinateurs critiques pour la sécurité nationale) a réuni un consortium international pour développer une plate-forme matérielle et logicielle basée sur l'ISA RISC-V pour les marchés de l'aviation et de l'aérospatiale .

En combinant un système sur puce multicœur du principal fournisseur de solutions spatiales Cobham Gaisler avec l'hyperviseur XtratuM qualifié de fentISS, De-RISC créera une plate-forme prête à l'emploi pour les futures applications aéronautiques et aéronautiques avec une technologie made in Europe.

Grâce aux techniques d’atténuation des interférences multicœurs éprouvées du Barcelona Supercomputing Center, la plate-forme offrira un fonctionnement hautes performances avec une interférence considérablement réduite. Dans le même temps, Thales, l'un des principaux acteurs mondiaux du marché de l'aviation et de l'espace, testera la plate-forme sur de vraies applications aérospatiales.

«Avec la première plate-forme entièrement européenne pour l'espace, basée sur RISC-V, De-RISC garantira l'accès aux technologies conçues en Europe pour les applications aérospatiales, contribuant ainsi au programme« Technologies pour la non-dépendance et la compétitivité européennes »dans ces domaines stratégiques. marchés », explique Paco Gomez Molinero, directeur général de fentISS et coordinateur du projet De-RISC.

L’utilisation de RISC-V contribuera également à l’avenir de la plate-forme, grâce à la prise en charge croissante de l’architecture ISA (Open-Source Instruction Set Architecture), alors que les architectures propriétaires PowerPC et SPARC, traditionnellement utilisées les systèmes spatiaux sont en perte de vitesse. De ce fait, l’industrie spatiale n’est pas en mesure d’exploiter les logiciels des domaines commerciaux, ce qui oblige à s’orienter vers des architectures présentes sur des marchés commerciaux plus volumineux. La plate-forme finale sera portable pour d'autres architectures et offrira également une tolérance aux pannes supérieure.

De-RISC est une action d'innovation de 30 mois partiellement financée par la Commission européenne et lancée avec un budget de 3 444 625 €.

Projet De-RISC

Commentaires récents