Après la fameuse carte de développement RISC-V Sipeed Longan Nano, SeeedStudio sort un nouveau kit de développement basé sur l'architecture RISC-V GigaDevice GD32V.

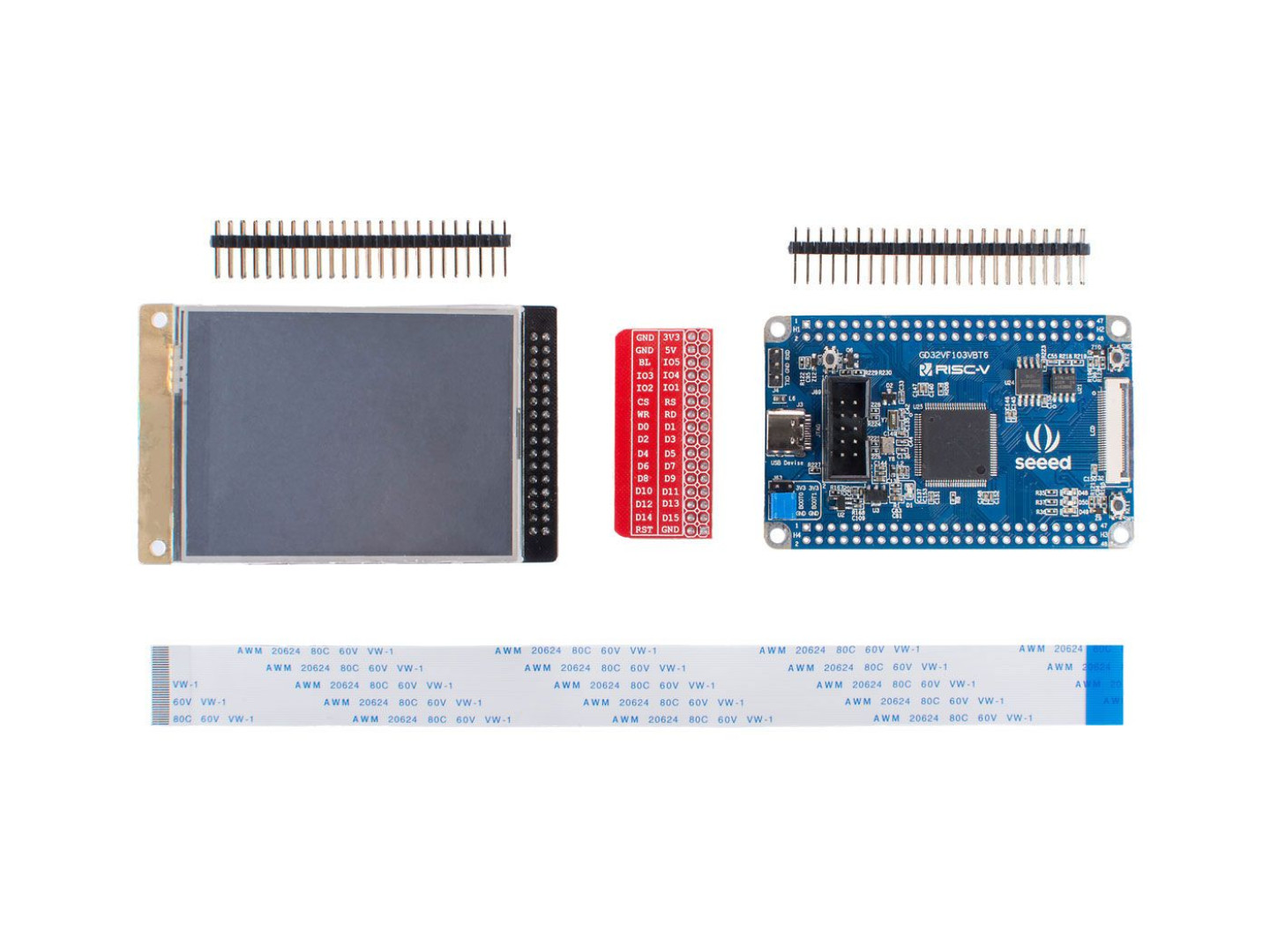

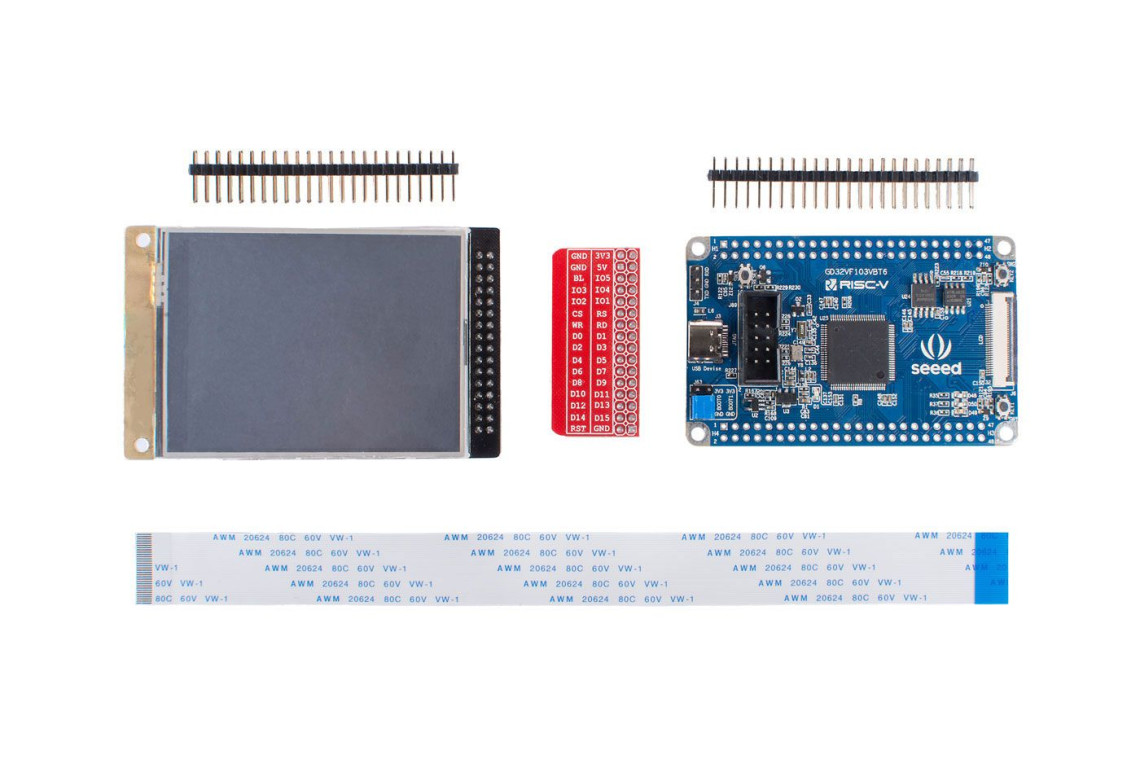

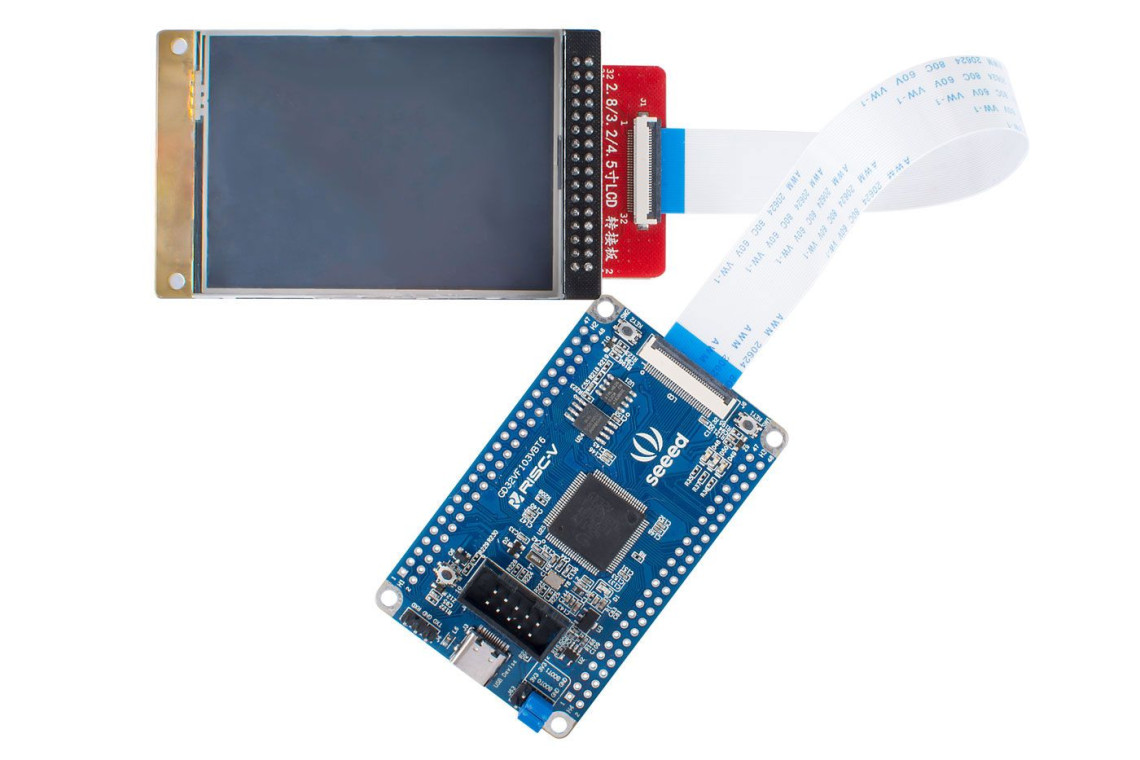

Ce kit contient une carte de développement SeeedStudio GD32 RISC-V et un écran LCD résistif de 2,8 pouces 240x320 pixels.

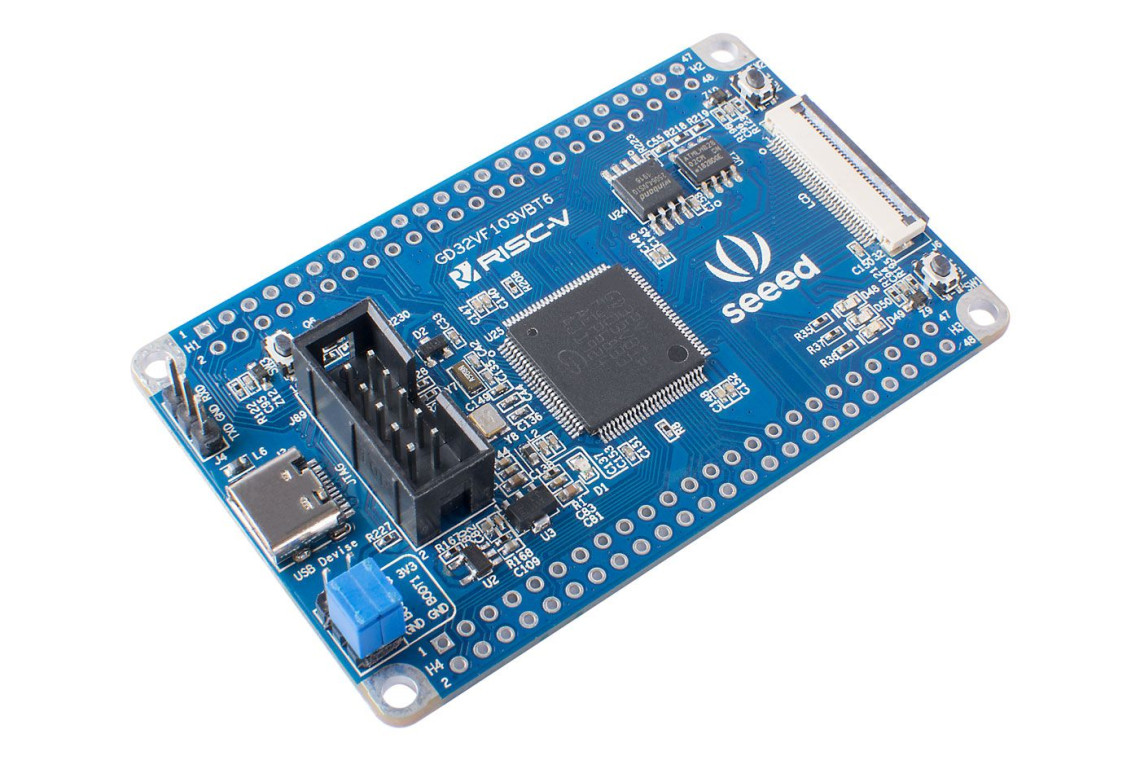

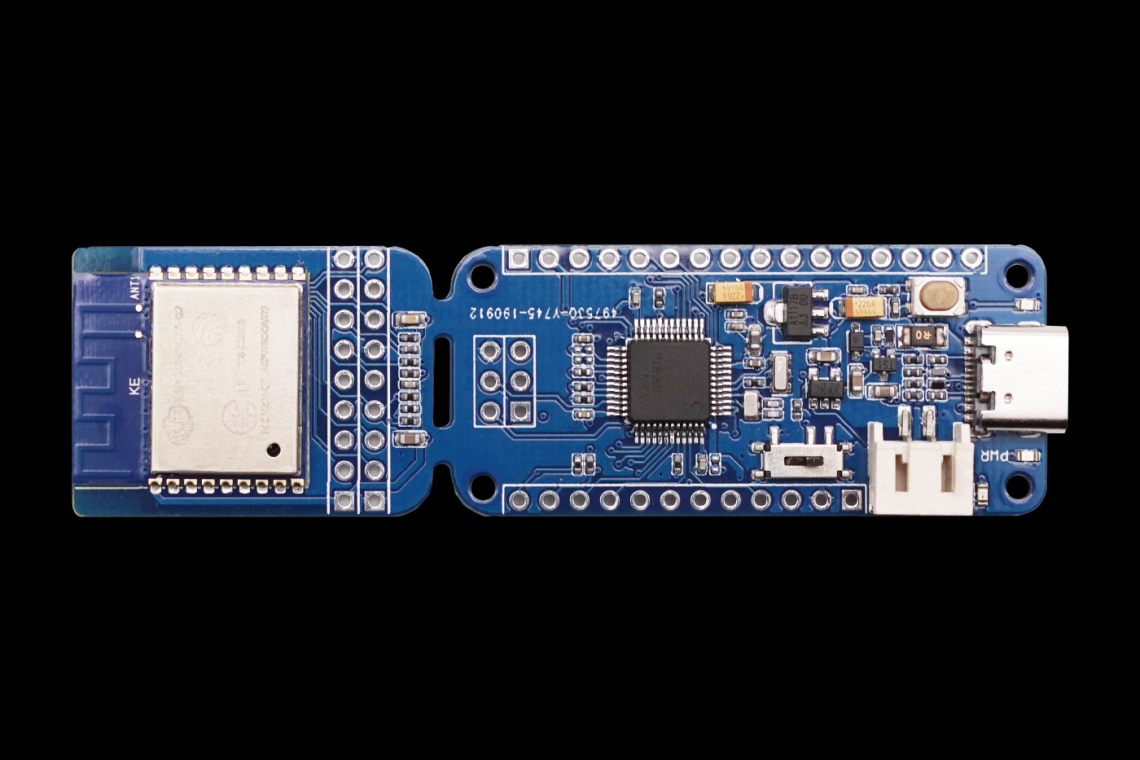

La carte de développement SeeedStudio GD32 RISC-V est basée sur le MCU GD32VF103VBT6 pouvant fonctionner à une fréquence pouvant atteindre 108 MHz. Le dispositif GD32VF103 est un microcontrôleur polyvalent 32 bits basé sur le cœur RISC-V. Il fournit une mémoire flash intégrée de 128 Ko et une mémoire SRAM de 32 Ko. Pendant ce temps, il fournit une richesse de ressources d'interface: 5 x U (S) ART, 2 x I2C, 3 x SPI, 2 x I2S, 2 x CAN2.0, 1 x USBFS.

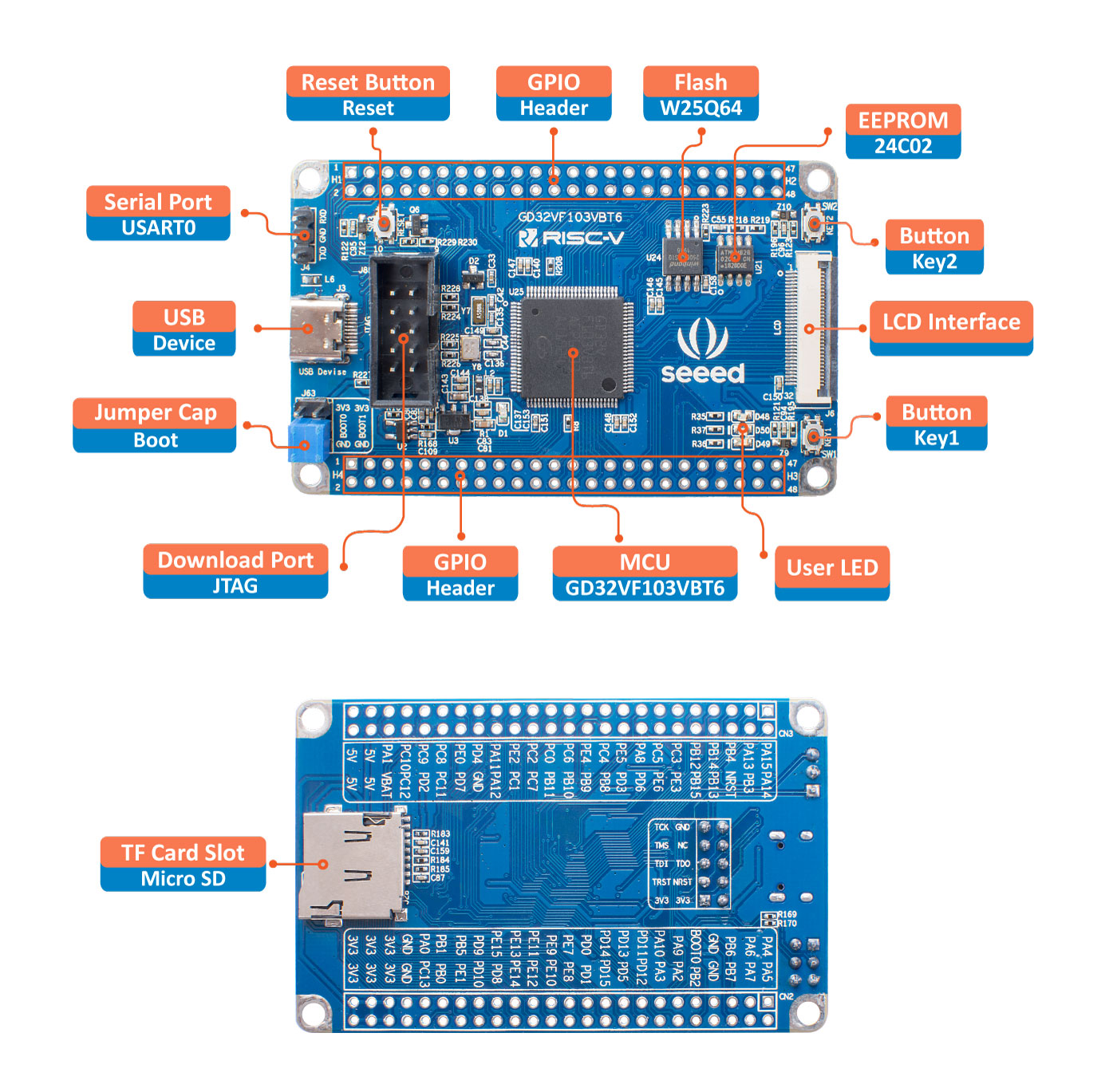

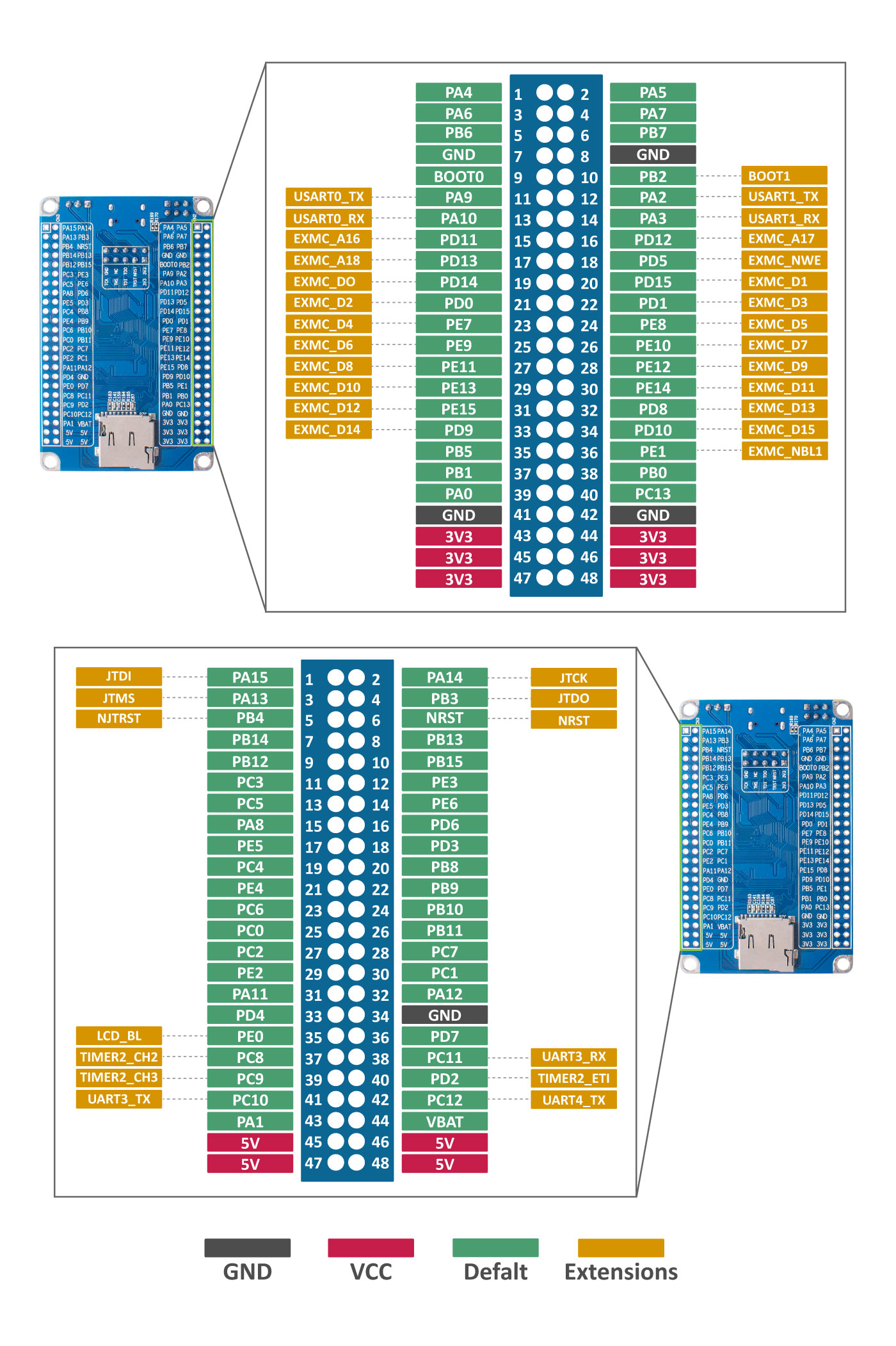

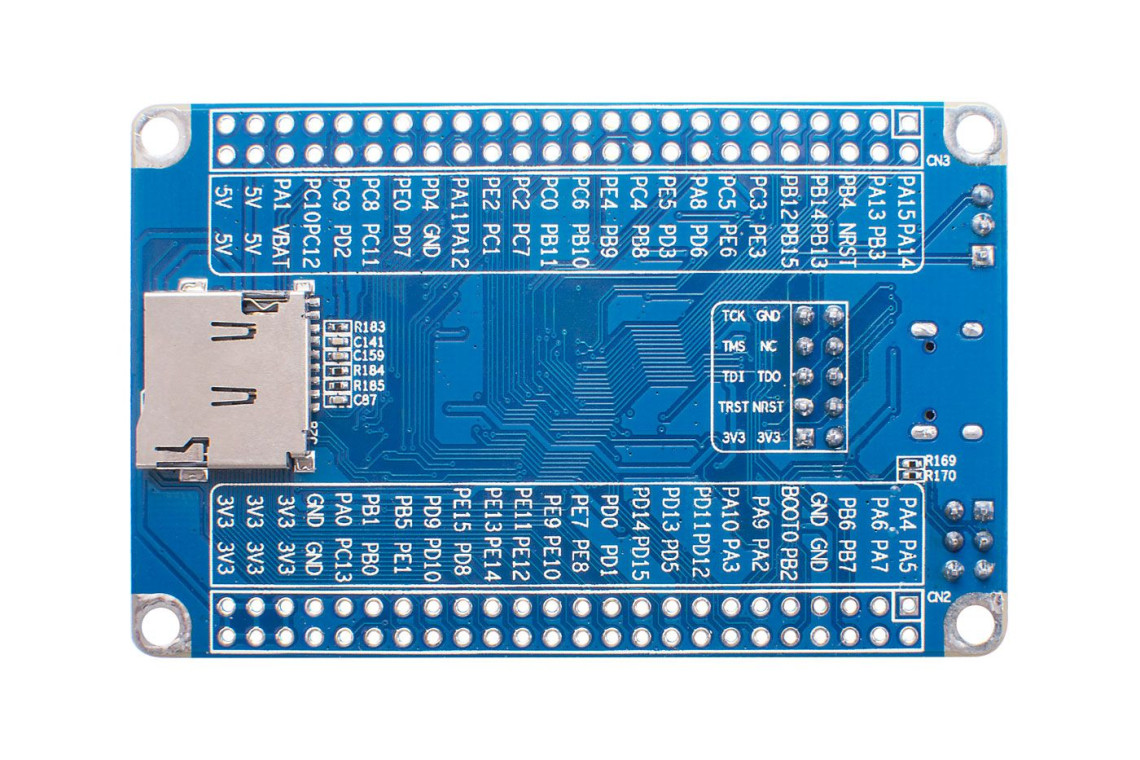

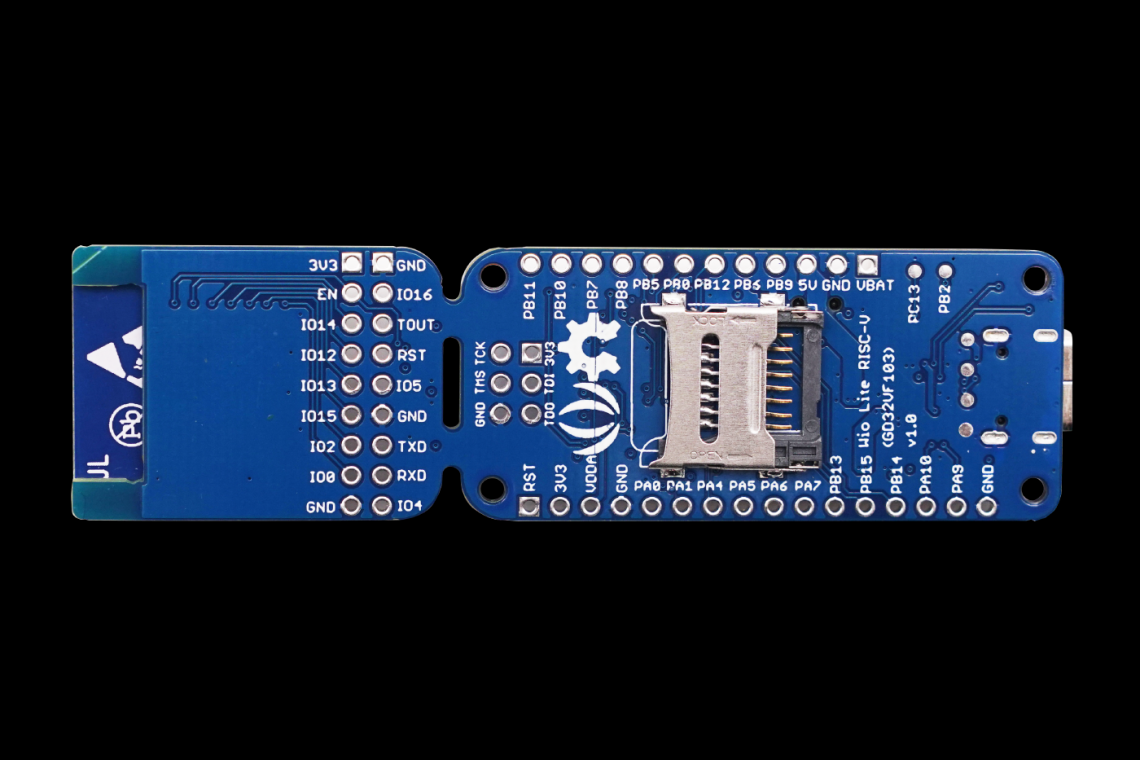

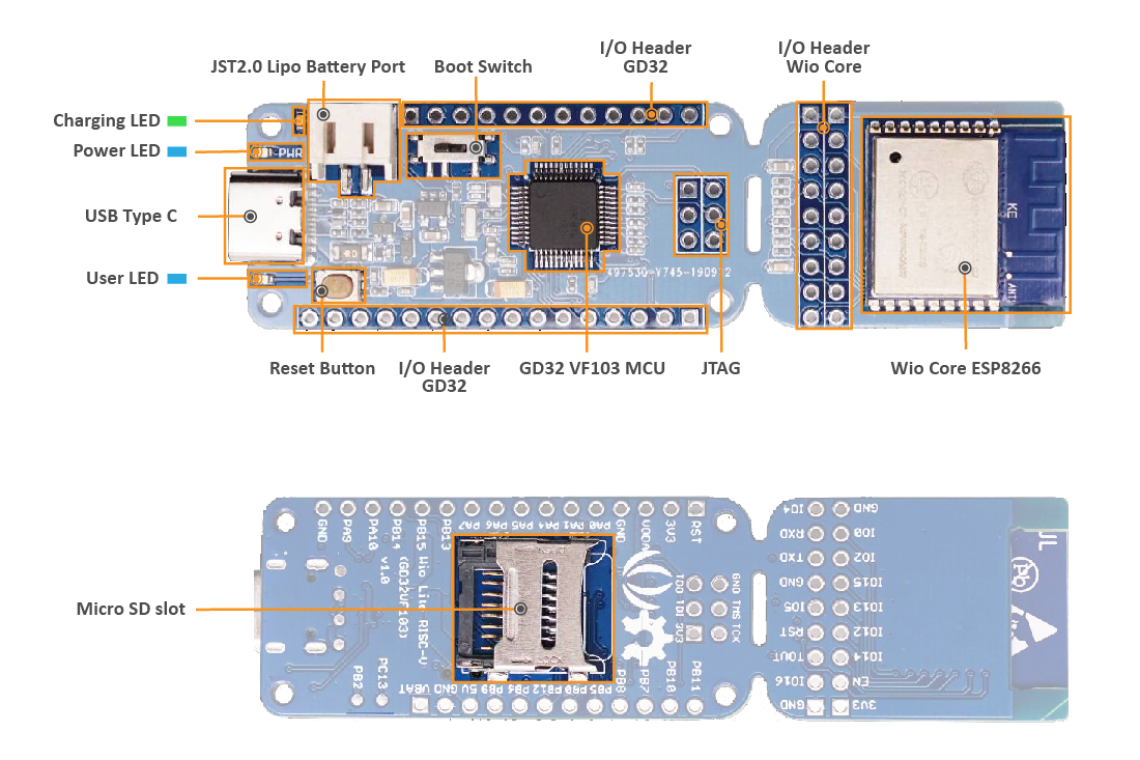

Nous décomposons tous les broches d’E / S (80 GPIO au total) du GD32VF103, ce qui répondra à vos divers besoins en développement. Avec la mémoire flash intégrée de 8 Mo et la mémoire EEPROM de 256 octets, vous pouvez implémenter des applications plus complexes. De plus, nous fournissons une multitude de ressources périphériques sur la carte de développement, notamment un écran LCD, un port USB de type c, un emplacement pour carte TF, deux boutons utilisateur et trois voyants utilisateur.

SeeedStudio a activement participé à l'écosystème logiciel RISC-V. Nous supportons l'EDI PlatformIO et le framework Arduino pour Seeedstudio GD32. Vous pouvez développer avec l'API Arduino que vous connaissez bien ou copier vos applications Arduino existantes et les compiler et les exécuter directement.

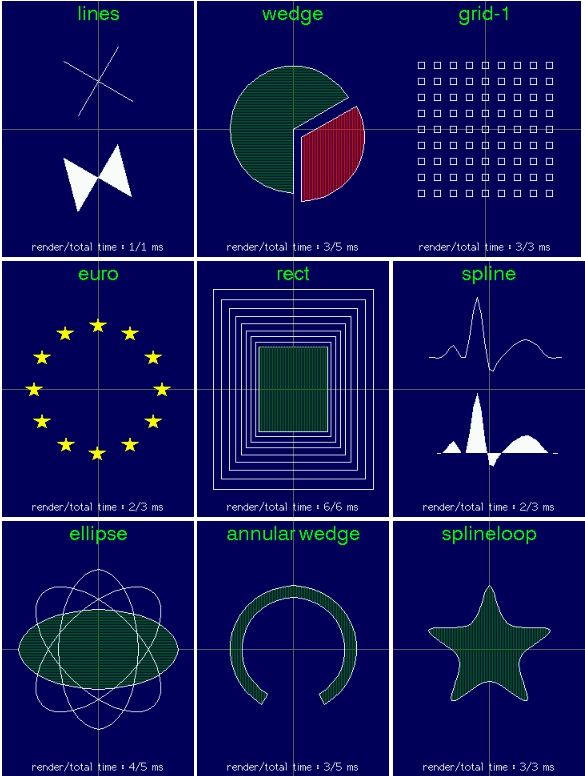

De plus, avec ce produit, nous avons apporté des surprises aux développeurs intéressés par RISC-V. Nous supportons Seeed_Arduino_LCD pour ce produit, qui est une interface utilisateur légère basée sur TFT_eSPI de Bodmer. Vous pouvez utiliser l'API TFT_eSPI pour développer vos propres produits. , et vous pouvez utiliser des applications basées sur TFT_eSPI et les exécuter directement.

Caractéristiques

- Microcontrôleur Gigadevice GD32VF103CBT6 RISC-V (rv32imac) à 108 MHz avec mémoire Flash de 128 Ko, SRAM de 32 Ko

- 8MB de mémoire Flash embarquée

- Stockage : Emplacement pour carte MicroSD

- Interface LCD: interface 16 bits 8080 et interface de commande à écran tactile SPI

- Interface GUI

- USB : 1x port USB Type-C pour l'alimentation et la programmation

- Alimentation : 5V via port USB Type-C

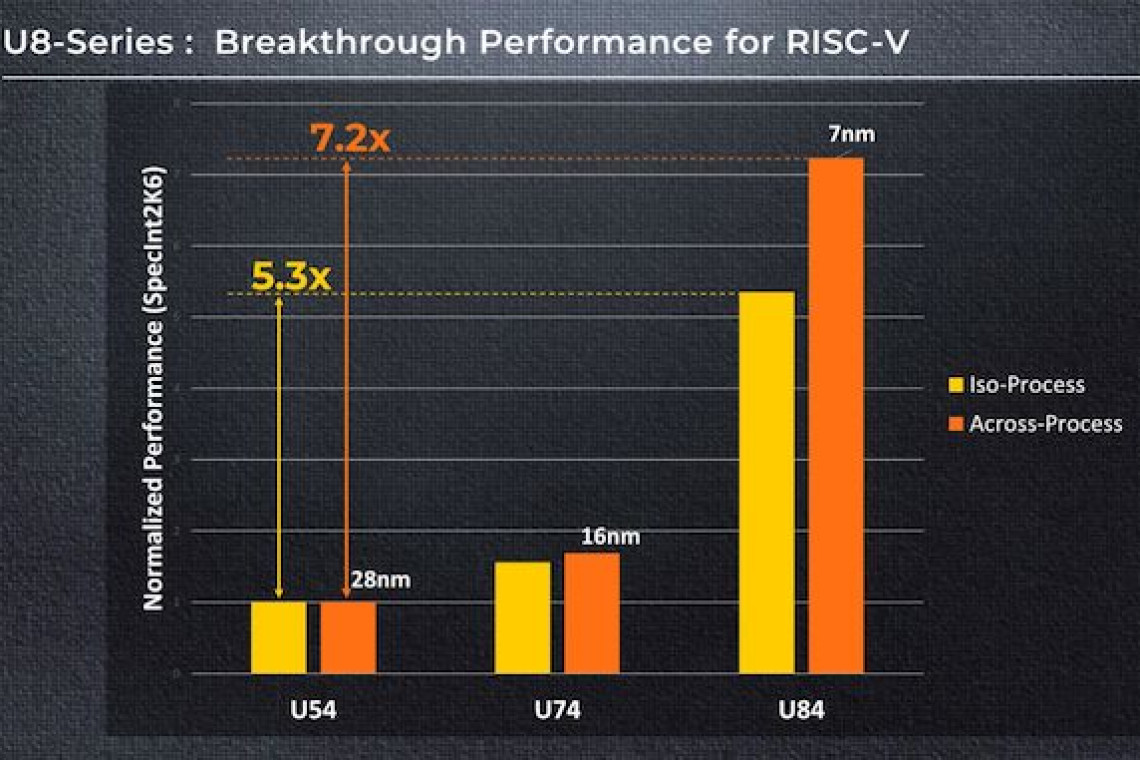

- Consommation électrique : La consommation électrique de base du RISC-V ne représente qu'un tiers de celle d'un Cortex-M3 traditionnel.

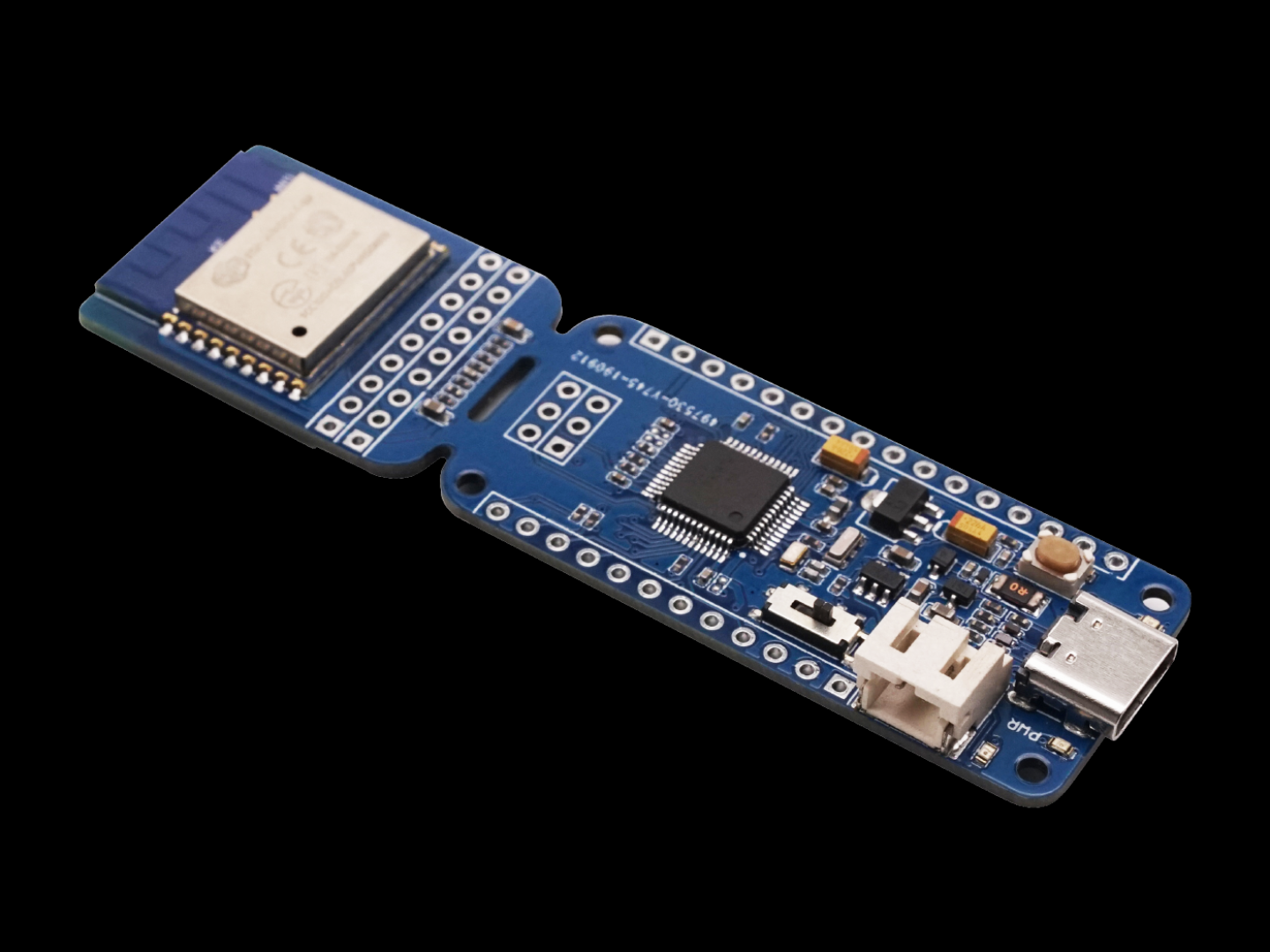

Vue d'ensemble du matériel

Connectique

Démo

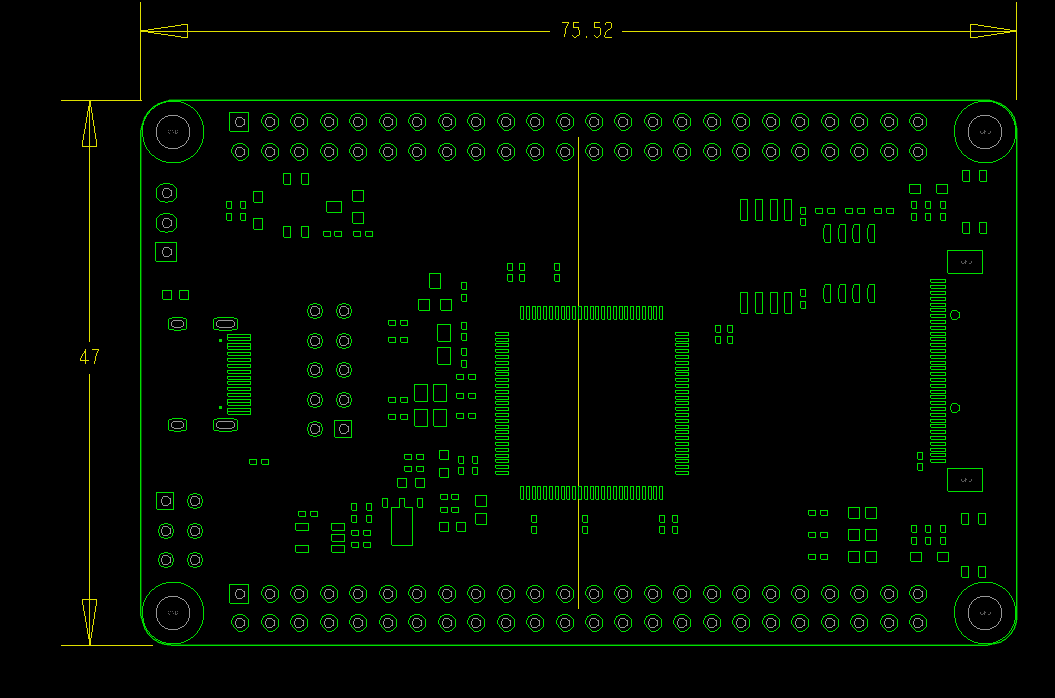

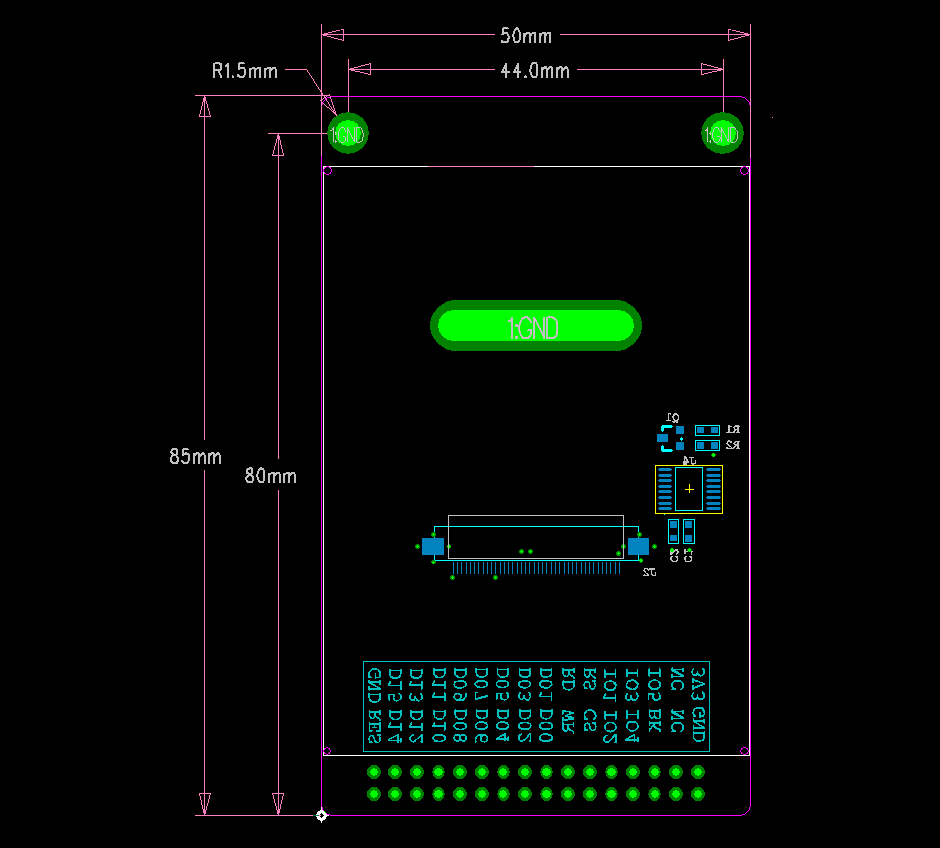

Dimensions de la carte

Dimensions de l'écran

Commentaires récents