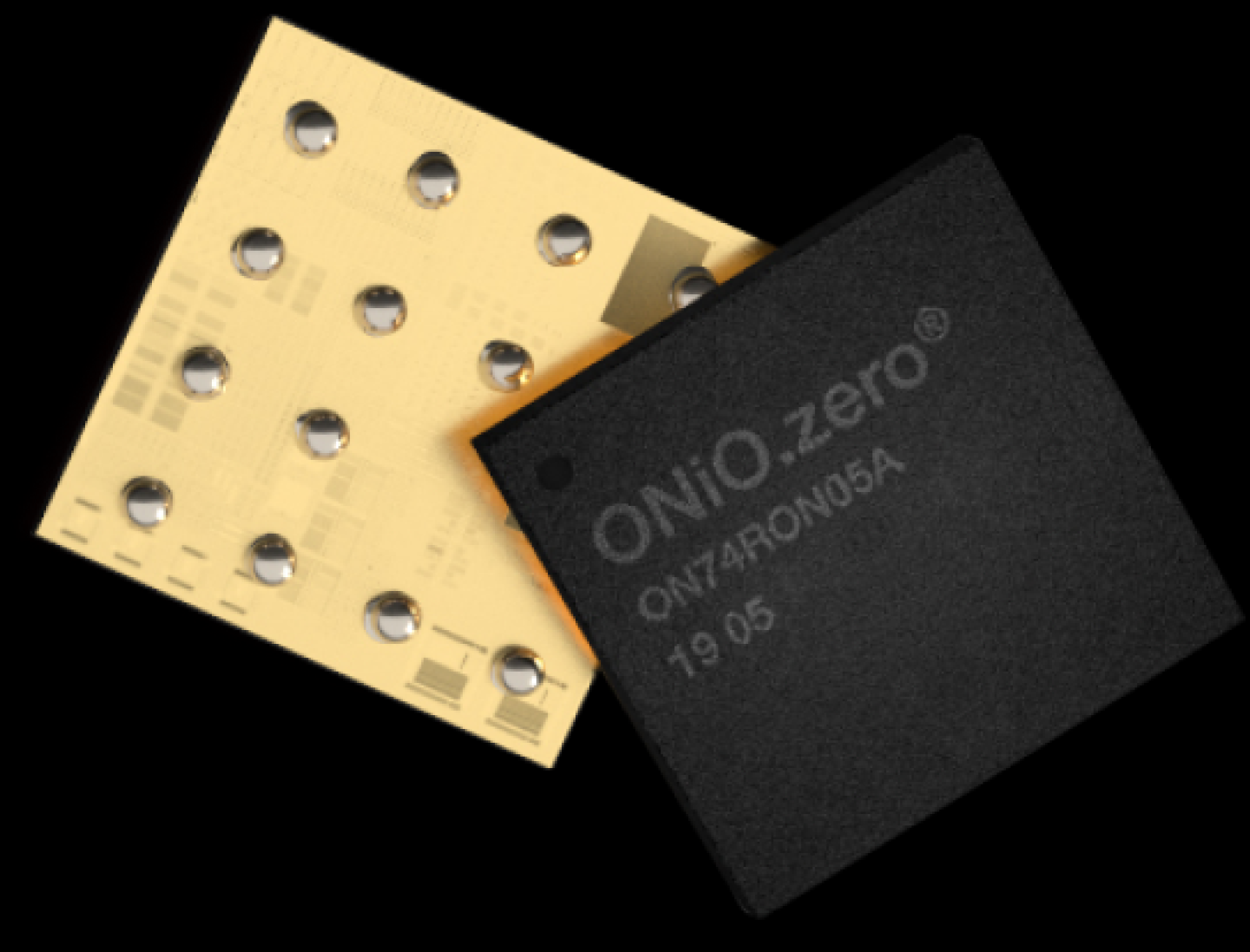

ONiO, le spécialiste norvégien de l'Internet des objets (IoT) axé sur les soins de santé, a annoncé ONiO.zero, un microcontrôleur à très faible puissance basé sur RISC-V capable de fonctionner entièrement à partir de l'énergie récoltée - sans avoir besoin d'une batterie ou d'une alimentation.

"ONiO.zero est un microcontrôleur sans fil à très faible consommation d'énergie qui utilise la technologie de récupération d'énergie (...) Cela signifie que l'ONiO.zero fonctionne uniquement avec l'énergie de son environnement. Pas de pile bouton, pas de supercap, pas de lithium, pas de batterie du tout - mais toujours une tonne de puissance."

"Les solutions basées sur la batterie s'accompagnent de la mise en garde inévitable du remplacement de la batterie, ce qui se traduit par un coût supplémentaire, tout au long de leur propriété. ONiO.zero contourne ce point douloureux et réduit le coût de propriété. Il peut être utilisé pour alimenter des capteurs et des appareils pendant des années, sans avoir à penser à l'entretien - déployez et oubliez. ONiO.zero est autoalimenté et prend en charge une large gamme de sources d'alimentation, des bandes RF multifréquences prenant en charge le GSM et l'ISM aux sources externes en option telles que l'énergie solaire, piézoélectrique, thermique et voltaïque cellules."

Le microcontrôleur lui-même est basé sur l'architecture du jeu d'instructions RISC-V gratuit et open source - en particulier, RV32EMC - fonctionnant jusqu'à 24 MHz lorsqu'il est alimenté à 1,8 V. Le contrôleur fonctionne également à des tensions plus faibles, lorsque cela est nécessaire: 1 V vous donne 6 MHz, 0,8 V vous donne 1 MHz, et la puce continuera à fonctionner - bien qu'à des vitesses toujours décroissantes - jusqu'à 450 mV, affirme la société. Il y a 1 Ko de ROM de masque et 2 Ko de RAM inclus, ainsi que 8 à 32 Ko de stockage flash ultra-basse consommation capable de 100 000 cycles d'écriture et lisible jusqu'à 850 mV.

L'ONiO.zero comprend également un émetteur Bluetooth Low Energy (BLE) sans cristal capable de fonctionner à des tensions aussi basses que 850 mV, un émetteur IEEE 802.15.4 ultra-large bande (UWB) fonctionnant dans la bande 3,5-10 GHz, et un émetteur radio MICS 433 MHz en option pour une utilisation industrielle, scientifique et médicale (ISM).

L'énergie de la puce est fournie gracieusement par un redresseur de radiofréquence interne, récupérant la puissance des bandes 800/900/1800 et 1900 / 2400MHz (ISM et GSM). Pour les environnements sans énergie radiofréquence suffisante pour alimenter la puce de manière fiable, la «fabrique d'énergie interne» prend en charge les cellules photovoltaïques jusqu'à 400 mV, les sources piézoélectriques et thermiques de 1,8 V à 3,6 V.

Plus d'informations sur ONiO.zero sont disponibles dans la fiche technique, publiée sur demande sur la page officielle du produit.

Commentaires récents