Cobham Gaisler a annoncé aujourd'hui lors du sommet RISC-V à San Jose, en Californie, qu'il allait lancer une nouvelle gamme de cœurs (IP) de processeur qui implémente l'architecture de jeu d'instructions RISC-V (ISA). Le noyau IP du processeur NOEL-V, le premier produit de la famille, sera mis à disposition le 25 décembre pour téléchargement dans les FPGA Kintex UltraSCALE de Xilinx.

Cobham est un membre de niveau or de la Fondation RISC-V, qui dirige le développement et l'adoption futurs de l'architecture de jeu d'instructions RISC-V (ISA), une architecture de jeu d'instructions ouverte et gratuite qui permet une nouvelle ère d'innovation de processeur grâce à l'open collaboration standard. Cobham a également annoncé aujourd'hui un nouveau cœur de processeur LEON5, élargissant ainsi son portefeuille de processeurs SPARC.

«Il a été facile de tirer parti de notre vaste expérience des précédents développements du processeur RISC pour les applications spatiales et de mettre tout cela dans la conception du nouveau processeur NOEL-V ciblant également les applications terrestres. Notre objectif a été de créer une solution qui peut rivaliser avec d'autres implémentations RISC-V et en même temps être utile pour nos clients spatiaux traditionnels. Et nous publions également la version de base dans la variante open source gratuite de notre bibliothèque de base IP VHDL, conformément à ce que nous avons fait dans le passé avec nos cœurs IP de processeur. », A déclaré Nils-Johan Wessman, chef de projet RISC-V, Cobham Gaisler.

«Cobham est ravi d'ajouter notre première implémentation en interne d'un cœur de processeur RISC-V à notre portefeuille de processeurs actuel», a déclaré Sandi Habinc, directeur général de Cobham Gaisler. «L'ajout d'une gamme de produits de processeurs RISC-V renforce les capacités de Cobham à offrir des solutions de processeur fiables à des clients également en dehors du domaine spatial.» Pour plus d'informations sur le processeur NOEL-V de Cobham Gaisler, veuillez visiter le site www.cobhamaes.com/noel-v.

«Depuis près de 20 ans, les processeurs LEON de Cobham, qui sont basés sur le SPARC ISA ouvert, ont été utilisés dans les solutions de microélectronique RadHard et High Reliability dans des centaines de vaisseaux spatiaux en raison de leur riche ensemble de fonctionnalités et de leur fiabilité», a déclaré Jan Andersson, directeur de l'ingénierie. , Cobham Gaisler. «Nous avons l'intention de lancer des produits basés sur le RISC-V ISA en parallèle avec le développement de nos produits basés sur des processeurs LEON SPARC, y compris le cœur de processeur LEON5.»

«Xilinx est heureux de voir Cobham Gaisler étendre son offre avec NOEL-V pour intégrer RISC-V ISA à son portefeuille IP de processeurs», a déclaré Simon George, directeur du marketing des plates-formes embarquées. «En tant qu'architecture de processeur open source émergente, NOEL-V est désormais une option viable pour le traitement de base souple dans notre portefeuille FPGA axé sur l'espace.»

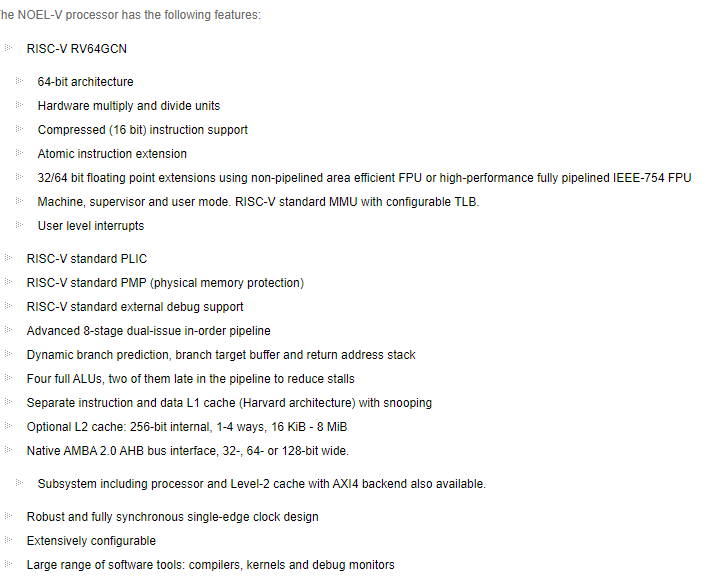

Le produit RISC-V initial sera un coeur (IP) de processeur compatible RV64GC, une architecture 64 bits, écrite en VHDL. Le processeur sera entièrement intégré à la bibliothèque de base IP GRLIB VHDL de Cobham. GRLIB offre une multitude d'interfaces et de fonctions telles que l'interconnexion série haute vitesse, le chiffrement, la compression, etc., auxquelles le processeur RISC-V peut s'interfacer. Il sera complété par la mise à niveau du moniteur de débogage logiciel GRMON3 pour prendre en charge la nouvelle ISA.